Floor Planning Placement And Routing In Vlsi

A bad floor plan will lead to waste age of die area and routing congestion.

Floor planning placement and routing in vlsi. The figure depicting floor plan die size µm of samm is shown beside. Power planning is a step done along with floorplanning inorder to distribute power with proper power drop analysis across the design so that entire design is getting power uniformly. It is a factor that directly affects the following in a design. Place and route is a stage in the design of printed circuit boards integrated circuits and field programmable gate arrays as implied by the name it is composed of two steps placement and routing the first step placement involves deciding where to place all electronic components circuitry and logic elements in a generally limited amount of space.

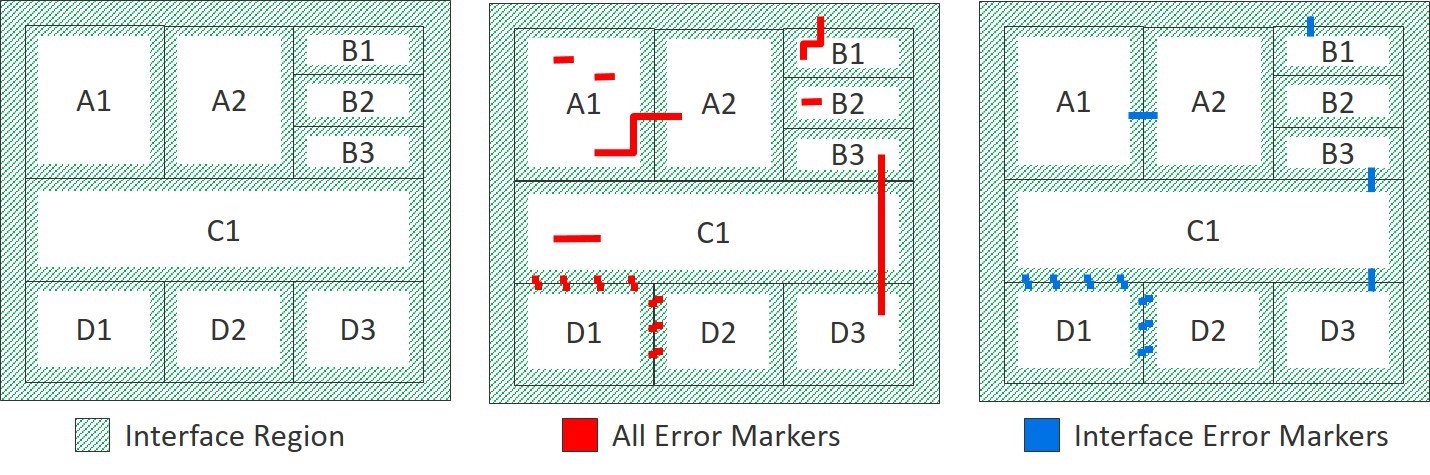

Routing placement and routing in vlsi routing in vlsi slides track assignment in vlsi routing in vlsi wiki switchbox routing in vlsi what is virtual routing in vlsi g cell in vlsi. Astro particularly uses the i o definitions from the tdf file in the starting phase of the design flow. Avoid criss cross placement of macros in order to save routing resources as well as from routing placement and congestion issues. Floorplanning is the most important stage in physical design.

Floor planning guide lines. Floor planning also decides the io structure aspect ratio of the design. Vlsichip is offering world class industry oriented vlsi design verification training program using cadence incisive enterprise simulator. Floor planning takes into account the macro s used in the design memory other ip cores and their placement needs the routing possibilities and also the area of the entire design.